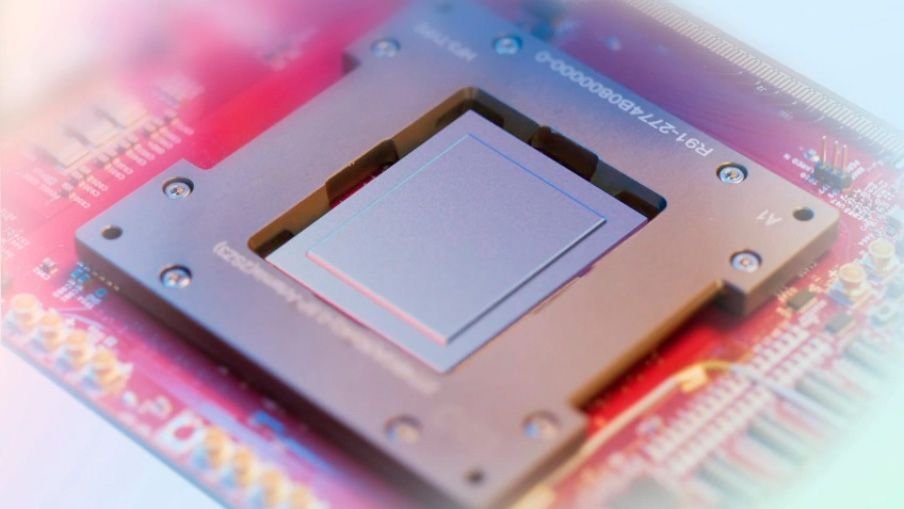

A Meta está testando seu primeiro chip AI baseado em RISC-V para treinamento de IA

A Meta foi uma das primeiras empresas a construir seus chips baseados em RISC-V para a inferência de IA há vários anos para reduzir custos e reduzir a dependência da NVIDIA. Reuters Relatos de que a empresa deu um passo adiante e projetou (presumivelmente com a assistência da Broadcom) seu acelerador interno para treinamento de IA. Se o chip atingir os objetivos da Meta, poderá reduzir sua dependência de GPUs NVIDIA AI de ponta-como H100/H200 e B100/B200-para o treinamento de modelos avançados de grande língua.

A Meta e a Broadcom gravaram o primeiro acelerador de treinamento de IA da Meta com o TSMC; Este último produziu as primeiras amostras de trabalho desses chips, e os parceiros criaram com sucesso a unidade, de acordo com o relatório. Até agora, a Meta começou com uma implantação limitada do acelerador, avaliando seu desempenho antes de aumentar a produção e a implantação. Não está claro se os engenheiros da Meta estão executando benchmarks no novo chip; Já foi implantado para fazer algum trabalho útil.

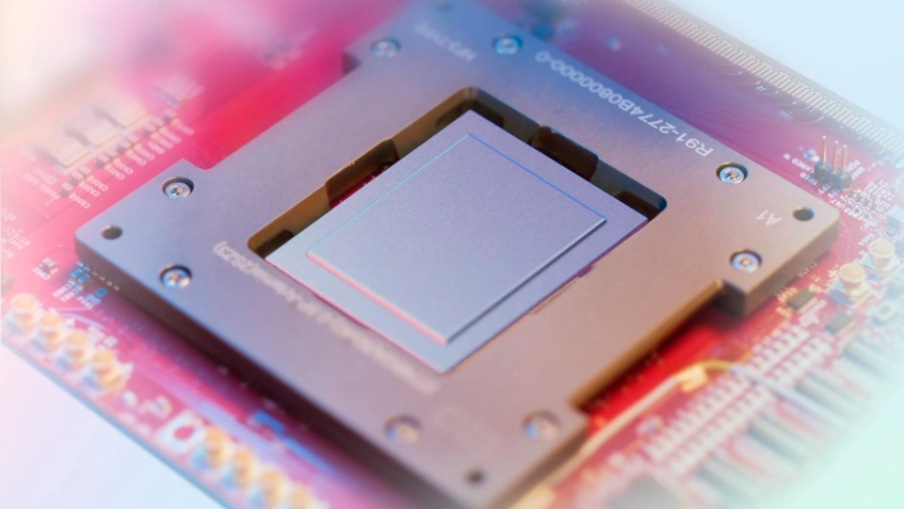

As especificações do chip são desconhecidas, embora normalmente, os chips de treinamento de IA usem um design conhecido como uma matriz sistólica. Essa arquitetura consiste em uma rede estruturada de elementos de processamento idênticos (PES) dispostos em linhas e colunas. Cada unidade lida com cálculos envolvendo matrizes ou vetores e os dados fluem sequencialmente através da rede.

Acelerador RISC-V personalizado para AI

Como o processador foi projetado para treinamento de IA – o que significa processar grandes quantidades de dados – espere que o processador apresente memória HBM3 ou HBM3E. Considerando que estamos lidando com um processador sob medida, a meta definiu seus formatos de dados e instruções suportadas para otimizar o tamanho da matriz, o consumo de energia e o desempenho. Quanto ao desempenho, o acelerador deve oferecer características competitivas de desempenho por watt com as GPUs AI atualizadas da NVIDIA, como H200, B200 e possivelmente B300 da próxima geração.

O chip é a mais recente adição ao programa Meta Treinamento e Inferência do Meta (MTIA). O programa enfrentou vários contratempos, inclusive quando o desenvolvimento foi interrompido em estágios semelhantes.

Por exemplo, descontinuou seu processador de inferência interna depois de não cumprir seus alvos de desempenho e energia durante testes limitados de implantação. Essa falha levou a Meta a mudar sua estratégia em 2022, fazendo grandes ordens para as GPUs da NVIDIA para atender aos seus requisitos imediatos de processamento de IA.

Desde então, a Meta se tornou um dos maiores clientes da NVIDIA, adquirindo dezenas de milhares de GPUs. Essas unidades têm sido críticas no treinamento de modelos de IA para recomendações, anúncios e a série Model Foundation LLAMA. Além disso, as GPUs da Green Company foram empregadas para processos de inferência, apoiando interações para mais de três bilhões de usuários diários em plataformas da Meta, de acordo com a Reuters.

Apesar desses desafios, a Meta continuou avançando em seu programa de silício personalizado. No ano passado, a Meta começou a usar um chip MTIA para tarefas de inferência e, olhando para o futuro, a liderança da Meta descreveu os planos de começar a usar seus chips personalizados para treinamento de IA até 2026. O plano é aumentar gradualmente o uso se o chip atingir as metas de desempenho e energia, que é um componente crítico do meta-meta de meta a longo prazo para projetar mais soluções de hardware personalizadas para as soluções de dados para os dados.

Uma coisa interessante a ser observada é que os aceleradores do MTIA para inferência usam núcleos de RISC-V de código aberto. Isso permite que a Meta personalize a arquitetura do conjunto de instruções, pois deseja atender aos seus requisitos em sua cadência, mas, por outro lado, não precisa pagar royalties a terceiros. Não está claro se o acelerador de treinamento da MTIA também se baseia no RISC-V ISA, mas isso é possível. Se isso for verdade, a Meta pode ter desenvolvido um dos chips baseados em RISC-V com maior desempenho do setor.