O JEDEC finaliza o padrão de memória HBM4 com as principais atualizações de largura de banda e eficiência

Jadec tem publicado A especificação oficial do HBM4 (Memória de largura de banda alta 4) sob o JESD238, um novo padrão de memória que visa acompanhar os requisitos de rápido crescimento das cargas de trabalho de IA, computação de alto desempenho e ambientes avançados de data center. O novo padrão apresenta alterações arquitetônicas e atualizações de interface que buscam melhorar a largura de banda de memória, a capacidade e a eficiência à medida que aplicativos com diferentes dados continuam a evoluir.

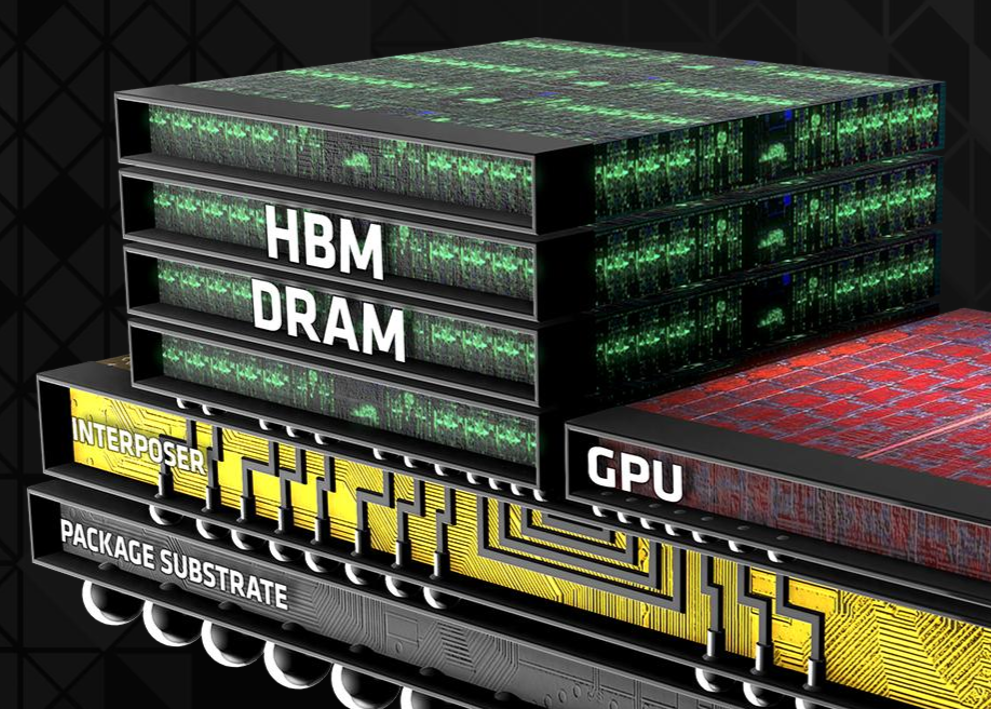

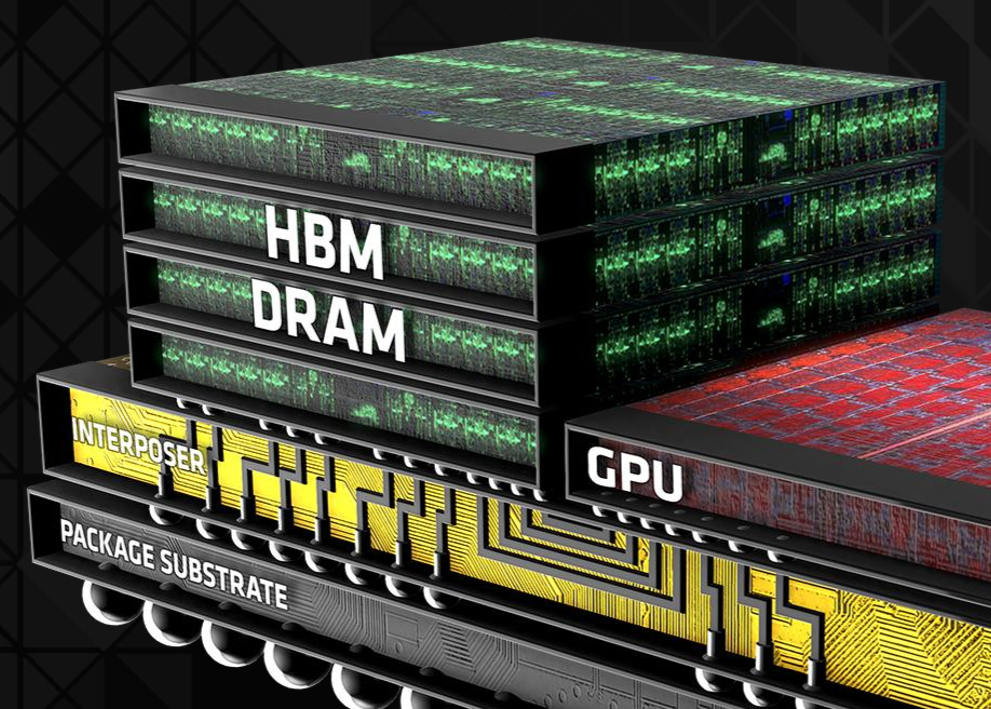

O HBM4 continua o uso de matrizes de DRAM empilhadas verticalmente, uma marca registrada da família HBM, mas traz uma série de melhorias em relação ao seu antecessor, o HBM3, com avanços significativos na largura de banda, eficiência e flexibilidade do projeto. Ele suporta velocidades de transferência de até 8 GB/s em uma interface de 2048 bits, fornecendo uma largura de banda total de até 2 TB/s. Uma das principais atualizações é a duplicação de canais independentes por pilha-de 16 no HBM3 a 32 no HBM4-cada agora com dois pseudo-channelos. Essa expansão permite maior flexibilidade de acesso e paralelismo nas operações de memória.

Em termos de eficiência de energia, a especificação JESD270-4 introduz o suporte para uma variedade de níveis de tensão específicos do fornecedor, incluindo opções de VDDQ de opções de 0,7V, 0,75V, 0,8V ou 0,9V e VDDC de 1,0V ou 1,05V. Diz -se que esses ajustes contribuem para o menor consumo de energia e melhoria a eficiência energética em diferentes requisitos do sistema. O HBM4 também mantém a compatibilidade com os controladores HBM3 existentes, permitindo que um único controlador opere com qualquer padrão de memória. Essa compatibilidade com versões anteriores facilita a adoção e permite projetos de sistemas mais flexíveis.

Além disso, o HBM4 incorpora o gerenciamento de atualização direcionado (DRFM), o que aprimora a mitigação de martelos de linha e suporta recursos mais fortes de confiabilidade, disponibilidade e manutenção (RAS). Na frente da capacidade, o HBM4 suporta configurações de pilha que variam de 4 a 16-alto, com densidades de matriz de drama de 24 GB ou 32 GB. Isso permite capacidades de cubo de até 64 GB usando pilhas de 32 GB de 16 altas, permitindo uma maior densidade de memória para cargas de trabalho exigentes.

Uma mudança arquitetônica notável no HBM4 é a separação dos barramentos de comando e dados, projetados para melhorar a simultaneidade e reduzir a latência. Essa modificação visa melhorar o desempenho em operações multicanais, que prevalecem nas cargas de trabalho de IA e HPC. Além disso, o HBM4 incorpora uma nova interface física e melhorias de integridade de sinal para suportar taxas de dados mais rápidas e maior eficiência do canal.

O desenvolvimento do HBM4 envolveu a colaboração entre os principais players do setor, incluindo Samsung, Micron e Sk Hynix, que contribuíram para a formulação do padrão. Prevê-se que essas empresas comecem a exibição de produtos compatíveis com o HBM4 em um futuro próximo, com a Samsung indicando planos de iniciar a produção até 2025 para atender à crescente demanda dos fabricantes de chips e hiperescaladores de IA.

À medida que os modelos de IA e os aplicativos HPC exigem maiores recursos computacionais, há uma crescente necessidade técnica de memória com maior largura de banda e maior capacidade. A introdução do padrão HBM4 deve atender a esses requisitos, descrevendo as especificações para tecnologias de memória de próxima geração, projetadas para lidar com os desafios de rendimento e processamento de dados associados a essas cargas de trabalho.